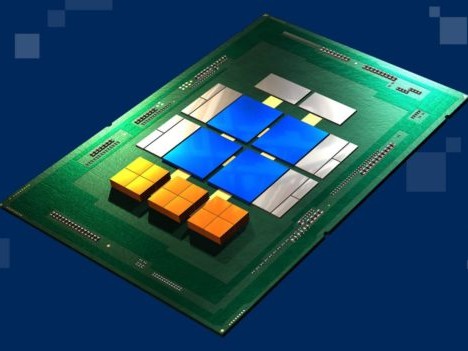

AMD Zen5架构的单核理论性能相比Zen4有望提升超过40%,这主要得益于AVX-512指令集的引入。这个指令集原本是Intel的特色技术,但从AMD Zen4架构开始,包括消费级的锐龙和数据中心级的霄龙都开始支持。然而,Intel的下一代Arrow Lake和Lunar Lake可能会放弃对AVX-512的支持,这使得AMD有机会独享这一技术。

在Zen4架构中,AVX-512是通过两个256位的FPU浮点单元组合执行的,这种方式虽然更灵活,功耗也较低,但性能并不是最优。而Zen5架构将会引入512位的FPU单元,可以直接执行AVX-512,这将大大提升性能,同时也能更高效地执行VNNI等指令,有利于提升AI表现。

为了配合这一升级,Zen5架构也将在其他方面进行改进,比如增大一级数据缓存DTLB的容量,从32KB增大到48KB,加宽载入存储队列,缩短FPU MADD的延迟周期等。此外,Zen5架构的整数执行流水线也将从8条增加到10条。

然而,Zen5架构的二级缓存容量将保持不变,每核心仍然是1MB。这些改进都有助于提升AMD Zen5架构的性能,使其在理论上比Zen4架构有超过40%的提升。

Apple 苹果 iPad Pro 2022款 11英寸 平板电脑(2388

Apple 苹果 iPad Pro 2022款 11英寸 平板电脑(2388

Lenovo 联想 拯救者 R7000P 2022 15.6英寸游戏本(R5-6600H、16GB、512GB、RTX3050、2.5k 165Hz)

Lenovo 联想 拯救者 R7000P 2022 15.6英寸游戏本(R5-6600H、16GB、512GB、RTX3050、2.5k 165Hz)

acer 宏碁 墨舞 EX214 2022款 14英寸轻薄笔记本(i5-1240P、16GB、512GB)

acer 宏碁 墨舞 EX214 2022款 14英寸轻薄笔记本(i5-1240P、16GB、512GB)

Apple 苹果 MacBook Air 13.3英寸笔记本电脑(M1、8GB、256GB)教育优惠版

Apple 苹果 MacBook Air 13.3英寸笔记本电脑(M1、8GB、256GB)教育优惠版

Lenovo 联想 小新 Pro 16 2023款 七代锐龙版 16.0英寸 轻薄本 鸽子灰

Lenovo 联想 小新 Pro 16 2023款 七代锐龙版 16.0英寸 轻薄本 鸽子灰

Apple 苹果 iPad Pro 2022款 11英寸 平板电脑(2388

Apple 苹果 iPad Pro 2022款 11英寸 平板电脑(2388

BBK 步步高 S6 12.7英寸学生平板电脑 8GB+256GB Wi-Fi版 蓝黑色

BBK 步步高 S6 12.7英寸学生平板电脑 8GB+256GB Wi-Fi版 蓝黑色

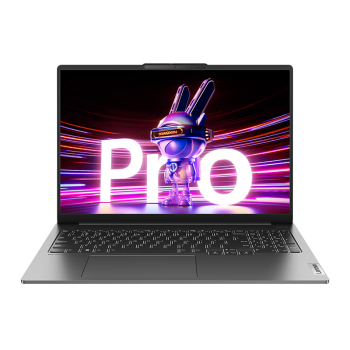

ThinkPad 思考本 ThinkBook 16+ 2024 锐龙版 16英寸轻薄本(R7-8845H、32GB、1TB)

ThinkPad 思考本 ThinkBook 16+ 2024 锐龙版 16英寸轻薄本(R7-8845H、32GB、1TB)

京东百亿补贴:COLORFUL 七彩虹 iGame G-ONEPlus 31.5英寸一体机(i7-12700H、16GB、1TB、RTX 3060)

京东百亿补贴:COLORFUL 七彩虹 iGame G-ONEPlus 31.5英寸一体机(i7-12700H、16GB、1TB、RTX 3060)

网友评论