引言:AI时代的内存瓶颈与行业破局

在人工智能、大数据中心、高性能计算(HPC)飞速发展的今天,内存技术始终是制约算力释放的核心瓶颈。当前市场上的内存产品呈现“三足鼎立”格局:DDR系列凭借低成本、高兼容性占据通用计算市场,HBM(高带宽内存)以恐怖带宽成为高端AI芯片的“性能基石”,GDDR则凭借平衡的功耗与带宽垄断显卡显存领域。然而,这三者之间的“中间地带”始终存在空白——既要HBM级别的高带宽与大容量,又需控制成本以适配更多场景,这一需求随着AI算力向中端市场渗透愈发迫切。

2025年12月14日,全球半导体行业标准制定机构JEDEC正式披露,正在加紧制定全新内存标准“SPHBM4”(标准封装高带宽内存第四代)。这款定位介于传统DDR与高端HBM之间的新型内存,以“512-bit位宽实现HBM4级带宽”的颠覆性设计,填补了市场空白,有望重构全球内存产业的竞争格局。

内存市场的“中间地带”困境:DDR、HBM、GDDR的各自局限

要理解SPHBM4的战略意义,需先看清当前内存市场的“三强割据”现状与难以调和的矛盾。长期以来,三大内存技术各自为战,均存在无法覆盖的应用盲区。

DDR系列:通用市场的“性价比之王”,带宽短板凸显

DDR系列(从DDR4到DDR5)是当前PC、服务器、消费电子设备的主流内存选择,核心优势在于成熟工艺、极低单位容量成本及广泛兼容性。但在AI训练、实时数据分析等高性能场景中,DDR5的带宽短板暴露无遗。AI大模型训练需数据在内存与处理器间高频传输,DDR5的带宽仅为HBM的十分之一甚至更低,导致“算力等内存”的严重瓶颈。此外,DDR5并行传输架构在高频率下功耗控制难度大,难以适配边缘计算设备的能效比要求。

HBM系列:高端算力的“性能天花板”,成本居高不下

HBM自2013年推出以来,凭借堆叠式3D封装、超高位宽设计,成为高端AI芯片、GPU的“性能核心”。从HBM1到HBM4E,带宽持续飙升,HBM4单堆带宽突破1TB/s,单堆容量最高达32GB,HBM4E更是将容量提升至64GB,带宽突破1.2TB/s。

然而,HBM的极致性能背后是高昂成本。其采用的硅中介层技术、TSV堆叠工艺及严格封装要求,使得单颗HBM芯片成本极高。此外,HBM的1024-bit/2048-bit超高位宽会占用大量芯片面积,限制单颗芯片堆叠数量,进而制约设备总容量上限。这导致HBM仅能应用于英伟达H100、AMD MI300等高端AI加速卡,难以普及到中端算力设备。

GDDR系列:显卡显存的“专属选择”,场景局限明显

GDDR作为显卡专用显存,平衡了带宽、功耗与成本,从GDDR5到GDDR7,带宽已提升至每秒数百GB,能满足3D渲染、游戏、视频编解码等图形处理需求。是当前消费级显卡与专业图形卡的核心配置。

但GDDR的设计初衷是适配图形计算的并行数据传输需求,在通用计算场景中能效比偏低。此外,GDDR的封装形式与接口标准相对固定,难以适配AI计算所需的大容量、高带宽协同工作模式,且成本虽低于HBM,但远高于DDR,单颗容量有限,无法满足数据中心对内存容量的规模化需求。

三大技术的局限,催生了市场对“中间态内存”的迫切需求——既要有HBM级别的带宽与容量,又需控制成本至DDR与HBM之间,同时具备良好兼容性。SPHBM4的诞生,正是为了填补这一空白。

SPHBM4技术解密:打破性能与成本的平衡困局

JEDEC推出的SPHBM4,全称“标准封装高带宽内存第四代”,核心创新在于通过4:1串行技术,在大幅降低位宽的同时,保持HBM4级别的性能与容量,兼容传统有机基板,实现成本与性能的精准平衡。

核心突破:4:1串行技术重构位宽与带宽的关系

HBM系列实现超高带宽的核心是1024-bit甚至2048-bit的超高位宽设计(带宽=位宽×频率÷8),但超高位宽带来芯片面积占用大、封装难度高、成本飙升的代价。

SPHBM4的革命性创新在于采用4:1串行技术,将传统HBM4的2048-bit位宽压缩至512-bit,同时通过优化数据传输协议或提升传输速率,最终实现512-bit位宽即可达到完整HBM4级别带宽。

这一突破带来多重优势:减少芯片面积占用,为容量扩展奠定基础;简化内存控制器设计,减少信号干扰,提升产品良率;串行传输架构在高频场景下功耗控制更具优势,为能效比优化提供空间。

关键参数:容量、封装与兼容性的全面升级

SPHBM4封装内部采用业界标准基础Die与HBM4 Die,单堆叠容量看齐HBM4、HBM4E,最高可达64GB。因位宽降低后芯片面积占用减少,理论上可通过多堆叠设计将总容量扩展至HBM4的四倍。

HBM高成本的核心原因之一是依赖硅中介层实现Die与基板的连接,而硅中介层材料与加工成本极高。SPHBM4突破性兼容传统有机基板,无需昂贵中介层,仅通过配套基片接口即可实现信号传输,大幅降低封装成本。同时,其保留堆叠式设计、TSV硅通孔技术与先进封装集成技术,确保性能稳定,成本介于DDR5与HBM4之间。

SPHBM4设计之初便考虑生态兼容性,兼容传统有机基板意味着现有服务器、AI加速卡的基板设计无需大幅重构,仅需优化接口协议即可支持,降低终端厂商迁移成本。此外,简化后的控制器设计与现有内存控制器适配难度低,有助于加快产品落地速度。

行业逻辑与应用前景:SPHBM4将重构哪些领域?

SPHBM4的推出是JEDEC基于AI算力普及需求的精准布局,应用前景主要集中在三大领域:

中端AI加速卡:打破“高端用HBM,低端用DDR”的二元格局

当前AI加速卡市场两极分化:高端产品搭载HBM4,性能强劲但单价数十万元,仅被大型科技公司、科研机构采用;中低端产品依赖DDR5,性能不足,难以支撑大模型推理与训练。

SPHBM4让中端AI加速卡厂商既能获得HBM4级带宽,满足中等规模AI模型需求,又将成本控制,使产品单价降至数万元级别,覆盖中小企业、边缘计算节点、行业专用AI设备等广阔市场。

数据中心服务器:解决“带宽-容量-成本”的三角难题

数据中心对内存的核心需求是“高带宽、大容量、低成本”。当前DDR5带宽不足导致数据处理延迟高,HBM成本过高难以规模化部署。SPHBM4“带宽媲美HBM4、容量超DDR5、成本居中”的特性完美适配数据中心需求。

边缘计算设备:平衡性能与功耗的最优解

边缘计算设备(智能网关、工业物联网终端、自动驾驶域控制器)的核心需求是“有限功耗下提供足够计算与存储性能”。当前DDR5带宽不足限制实时数据处理能力,HBM高功耗与高成本无法适配边缘场景。SPHBM4的中低功耗、高带宽特性成为理想选择

挑战与争议:SPHBM4能否真正打破市场格局?

尽管SPHBM4优势显著,但要实现市场普及,仍需面对挑战:

成本控制与规模化量产的考验

SPHBM4成本虽低于HBM4,但仍高于GDDR7与DDR5,规模化量产能力直接决定其市场竞争力。TSV技术、先进封装的良率控制,以及有机基板供应链稳定性,都是制约成本降低的关键。若量产良率低于预期,成本可能高于市场预期,影响终端厂商采用意愿。

行业生态的适配与兼容

内存技术普及离不开上下游生态支持,芯片组、服务器、AI加速卡厂商需针对性优化控制器接口、固件协议等。尽管SPHBM4兼容有机基板,但生态适配进度滞后可能导致“产品量产但设备不支持”的尴尬。同时,JEDEC标准制定进度至关重要——目前SPHBM4仍处于制定阶段,正式发布与量产时间未明确,若进度延迟,可能被其他技术抢占先机。

结语

JEDEC推出的SPHBM4内存标准,是基于行业需求痛点的创新性补位,而非对现有技术的简单替代。它以4:1串行技术为核心,实现“位宽降低但带宽不减”的突破,通过兼容有机基板、优化封装设计,平衡了性能、容量、成本与功耗四大维度,填补了DDR与HBM之间的市场空白。

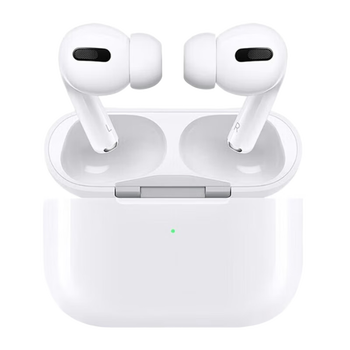

萨勒芬妮【直营正品丨Pro2顶配】华强北蓝牙耳机适用苹果安卓真无线降噪Airpods超长续航入耳式运动游戏IOS 千元音效丨双耳主动降噪

萨勒芬妮【直营正品丨Pro2顶配】华强北蓝牙耳机适用苹果安卓真无线降噪Airpods超长续航入耳式运动游戏IOS 千元音效丨双耳主动降噪

OPPO Reno14 高清长焦实况照片 Live图神机 新款5G智能 学生拍照 AI手机 【国家补贴】 人鱼姬 12GB+256GB 全网通 官方标配

OPPO Reno14 高清长焦实况照片 Live图神机 新款5G智能 学生拍照 AI手机 【国家补贴】 人鱼姬 12GB+256GB 全网通 官方标配

邦克仕(Benks)适用小米 15?Ultra手机保护壳 小米 15?Ultra防摔磁吸壳 轻砂壳男女通用款保护套不沾指纹 黑

邦克仕(Benks)适用小米 15?Ultra手机保护壳 小米 15?Ultra防摔磁吸壳 轻砂壳男女通用款保护套不沾指纹 黑

小米红米K80至尊版 【国家补贴】新品5G小米手机 REDMI红米手机 砂岩灰 12GB+256GB 【官方标配】

小米红米K80至尊版 【国家补贴】新品5G小米手机 REDMI红米手机 砂岩灰 12GB+256GB 【官方标配】

图拉斯三合一充电宝【小巧便携 | 低温快充】3c认证随心充自带插头伸缩线能量棒10000毫安苹果17可上飞机 【mini便携·超级快充】1万毫安 | 樱花粉 【品牌直营】自动蓄电 | 电量显示 | 便捷挂绳

图拉斯三合一充电宝【小巧便携 | 低温快充】3c认证随心充自带插头伸缩线能量棒10000毫安苹果17可上飞机 【mini便携·超级快充】1万毫安 | 樱花粉 【品牌直营】自动蓄电 | 电量显示 | 便捷挂绳

天钡GT37迷你主机AI PC高性能锐龙HX370电脑台式机 高算力电竞游戏便携MINI小型口袋整机带OCuLink接口 锐龙AI9 HX370「强大算力」 32G LPDDR5内存1TB固态硬盘

天钡GT37迷你主机AI PC高性能锐龙HX370电脑台式机 高算力电竞游戏便携MINI小型口袋整机带OCuLink接口 锐龙AI9 HX370「强大算力」 32G LPDDR5内存1TB固态硬盘

海康威视(HIKVISION)无线wifi监控摄像头 家用室内外双500万像素360度无死角带夜视 防尘防水手机远程监视器Q4PADM-W

¥419

¥439

海康威视(HIKVISION)无线wifi监控摄像头 家用室内外双500万像素360度无死角带夜视 防尘防水手机远程监视器Q4PADM-W

¥419

¥439

中国移动移动流量卡5G全国不限速手机卡电话卡低月租无限流量卡大流量上网卡大王卡 宝藏卡丨19元185G全国通用流量丨全国可发

中国移动移动流量卡5G全国不限速手机卡电话卡低月租无限流量卡大流量上网卡大王卡 宝藏卡丨19元185G全国通用流量丨全国可发

赛睿(SteelSeries)【Faker冠军同款】寒冰Nova5无线耳麦2.4G/蓝牙双无线 游戏电竞笔记本电脑头戴式耳机 FPS 吃鸡

赛睿(SteelSeries)【Faker冠军同款】寒冰Nova5无线耳麦2.4G/蓝牙双无线 游戏电竞笔记本电脑头戴式耳机 FPS 吃鸡

网友评论