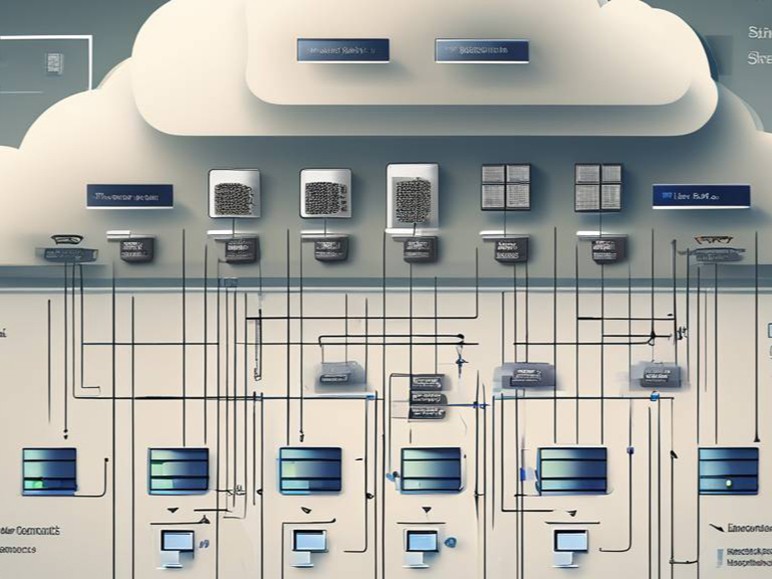

半导体知识产权(IP)在现代片上系统(SoC)设计中起着至关重要的作用。这并不奇怪,因为现代SoC是高度复杂的设计,利用了已经证明的构建模块,如处理器、接口、基础IP、片上总线结构、安全IP等。这反映在蓬勃发展的第三方知识产权市场,到2023年可达到70.5亿美元。

到2023年,新思科技(Synopsys)的设计IP收入约为15.4亿美元,在全球第三方IP细分市场中排名第二,并且是接口IP和基础IP的领导者。该公司并非一蹴而就。随着时间的推移,新思科技采取了深思熟虑的战略方法来建立自己的知识产权业务。在过去的25年里,新思科技努力培养了世界上最广泛的IP组合,包括构建模块/外设、接口、基础IP(标准单元、存储器)、处理器、安全性、人工智能加速器(NPU、DSP)、传感器等。值得注意的是,虽然第三方IP市场在2022年至2023年间的增长率略高于6%,但新思科技的设计IP业务增长率约为18%。该公司重申并再次承诺其设计IP业务的可持续增长率为15%左右。

以客户为中心的方法

新思科技成功的核心在于其对客户满意度的坚定承诺。凭借无与伦比的IP质量、卓越的支持和可靠的声誉,Synopsys赢得了全球半导体和系统公司的信任。来自行业合作伙伴和客户的赞誉强调了Synopsys作为半导体IP解决方案首选的声誉。

新思科技继续重申其卓越的承诺,优先考虑质量,创新和客户支持。该公司继续通过将有机开发的IP和收购的IP添加到其投资组合中来证明其投资承诺。最近的几个例子是新思科技通过收购Intrinsic ID推出的通用芯片互连快速(UCIe) IP和物理不可克隆功能(PUF) IP。这种战略扩张继续将新思定位为半导体设计领域值得信赖的合作伙伴,使客户能够充满信心地实现他们的设计目标。

多Die系统异构互操作的UCIe IP

随着异构计算架构的兴起以及人工智能和机器学习工作负载的激增,设计人员在设计产品时必须越来越多地考虑硅级和系统级优化。多Die系统是下一波系统创新的关键,可以将异构Die集成到单个封装中。通用芯片快速互连(UCIe)标准于2022年推出,以满足这种异构Die-to-Die互操作性需求。通过标准化小芯片(chiplet)之间的通信,UCIe不仅简化了集成过程,而且还促进了一个更广泛的生态系统,来自不同供应商的小芯片可以无缝地集成到一个设计中。

新思科技首席执行官Sassine Ghazi在新思科技用户组(SNUG)大会的主题演讲中强调了多模解决方案的重要性。他重点介绍了英特尔的Pike Creek,这是世界上第一个支持UCIe的芯片,是英特尔、台积电和新思科技合作的结果。

作为辅助点,随着异构SoC的发展,新思科技的EDA工具与其IP产品组合紧密集成,实现无缝互操作性和更快的上市时间。

用于安全的PUF IP

鉴于当今网络威胁日益复杂,半导体设计的完整性和安全性至关重要。随着连接设备的激增,确保敏感数据的机密性和完整性对于半导体制造商和系统集成商来说变得越来越重要。

新思科技最近完成了对PUF IP技术先驱Intrinsic ID的收购。PUF技术利用硅芯片的固有变化来生成唯一标识符,提供针对一系列安全威胁的强大保护,包括伪造、篡改和未经授权的访问。通过将Intrinsic ID的PUF IP集成到其产品组合中,新思科技使芯片设计人员能够将安全功能直接嵌入到他们的设计中,从而加快产品上市时间并降低成本。此次收购不仅扩大了新思科技的知识产权产品,而且丰富了其人才库,拥有一批经验丰富的研发工程师,他们对PUF技术有着深入的了解。新思科技打算利用Intrinsic ID在荷兰的存在,在埃因霍温建立一个PUF技术卓越中心,增强其在安全IP关键领域的研发能力。

原文《Synopsys Design IP for Modern SoCs and Multi-Die Systems》

HUAWEI 华为 手表watch gt4运动智能手表男女心率监测蓝牙电话微信手表 黑色氟橡胶表带

HUAWEI 华为 手表watch gt4运动智能手表男女心率监测蓝牙电话微信手表 黑色氟橡胶表带

Apple 苹果 iPad Air5 10.9英寸平板电脑 64GB WiFi版

Apple 苹果 iPad Air5 10.9英寸平板电脑 64GB WiFi版

iReader 掌阅 Ocean3 Turbo 7英寸电子书阅读器 4GB+64GB

iReader 掌阅 Ocean3 Turbo 7英寸电子书阅读器 4GB+64GB

AMD R7-5700X CPU 8核16线程 3.4GHz 散片

AMD R7-5700X CPU 8核16线程 3.4GHz 散片

Lenovo 联想 小新 24 五代锐龙版 23.8英寸 家用一体机 白色(R5-5500U、核芯显卡、8GB、512GB SSD)

Lenovo 联想 小新 24 五代锐龙版 23.8英寸 家用一体机 白色(R5-5500U、核芯显卡、8GB、512GB SSD)

MI 小米 13 5G手机 12GB+512GB 远山蓝

MI 小米 13 5G手机 12GB+512GB 远山蓝

RAZER 雷蛇 八岐大蛇 V2 2.4G蓝牙 双模无线鼠标 18000DPI

RAZER 雷蛇 八岐大蛇 V2 2.4G蓝牙 双模无线鼠标 18000DPI

FIREBAT 火影 T5A 五代锐龙版 15.6英寸 游戏本 黑色 (锐龙R5-5600H、RTX 3060 6G、16GB、512GB SSD、2.5K、IPS、165Hz)

FIREBAT 火影 T5A 五代锐龙版 15.6英寸 游戏本 黑色 (锐龙R5-5600H、RTX 3060 6G、16GB、512GB SSD、2.5K、IPS、165Hz)

PLUS会员:Xiaomi 小米 14Pro 5G手机 16GB+512GB

PLUS会员:Xiaomi 小米 14Pro 5G手机 16GB+512GB

网友评论