ASML公布了一种新型光刻工具的计划,该工具有望扩展高晶体管密度芯片的设计极限。ASML前总裁Martin van den Brink透露,全球研发机构Imec证实,新的“Hyper-NA”EUV技术处于早期开发阶段。今年早些时候,英特尔在俄勒冈州的半导体工厂安装了“Hyper-NA”系统。在安特卫普举行的Imec ITF世界上,van den Brink强调了加强照明系统和将生产率提高到每小时400-500片晶圆的必要性。高NA技术将数值孔径(NA)从0.33提高到0.55,预计将在10年内支持超越2纳米的工艺节点。现在,ASML的目标是到2030年推出Hyper-NA,达到0.75 NA。

正如Imec高级模式计划主任Kurt Ronse所指出的,这标志着Hyper-NA EUV首次纳入ASML的路线图。与ASML合作超过30年的Ronse承认正在进行超过0.55 NA的研究,目标是达到0.85 NA。这一进步的一个重大挑战是光偏振。超过0.55 NA,极化会降低对比度,需要使用偏振片,不幸的是,这会降低功率效率并增加生产成本。ASML仍然是高密度晶体管芯片所需的EUV工具的唯一制造商,通过台积电为英伟达、苹果和AMD等大客户提供服务。

英特尔最近安装了第一个Hyper-NA光刻系统,提高了分辨率和功能扩展,超越了英特尔的18A工艺节点,可与台积电的2nm工艺相媲美。台积电目前依赖于现有的EUV工具的双重模式,实现精确的边缘放置对齐-英特尔旨在通过更高分辨率的高na EUV绕过这项技术。

其他领先的芯片制造商,如三星、美光和SK海力士也在探索Hyper-NA技术,预计该技术足以满足从2nm到7埃的工艺节点过渡。最终,Hyper-NA将逐步进入市场,降低需要重复处理的双重图案的成本和复杂性。

Hyper-NA的替代品,如纳米压印光刻,与Hyper-NA扫描仪相比,吞吐量较低。在荷兰Mapper公司退出市场后,消除昂贵光罩的多光束电子束光刻技术也面临挑战。

除了光刻技术,进一步小型化晶体管的尝试已经接近物理极限。在接近2埃的尺度上,出现了基本的限制,需要具有更高电子迁移率的新材料来取代硅。这些材料对沉积和蚀刻提出了挑战,需要新的技术和设备。尽管有这些进步,硅片仍将是基础,只有特定的层利用新材料来增强电子流。

SoundCore 声阔 Life Q20i 头戴式无线蓝牙耳机

SoundCore 声阔 Life Q20i 头戴式无线蓝牙耳机

京东京造 JZZBZJ-001 手机支架 黑色

京东京造 JZZBZJ-001 手机支架 黑色

Doublepow 倍量 4槽充电器+6节5号电池+6节7号电池

Doublepow 倍量 4槽充电器+6节5号电池+6节7号电池

SHOKZ 韶音 OpenRun Pro 基普乔格 骨传导挂耳式降噪蓝牙耳机 EK橙

SHOKZ 韶音 OpenRun Pro 基普乔格 骨传导挂耳式降噪蓝牙耳机 EK橙

COLORFUL 七彩虹 iGame GeForce RTX 3080 Ultra W OC 10G LHR 显卡 10GB 白色 锁算力版

COLORFUL 七彩虹 iGame GeForce RTX 3080 Ultra W OC 10G LHR 显卡 10GB 白色 锁算力版

HUAWEI 华为 WATCH GT4 智能手表 46mm 曜石黑 氟橡胶表带

HUAWEI 华为 WATCH GT4 智能手表 46mm 曜石黑 氟橡胶表带

MI 小米 P27QBC-RG 27英寸 IPS FreeSync 显示器(2560×1440、165Hz、100%sRGB、HDR400、Type-C 65W)

MI 小米 P27QBC-RG 27英寸 IPS FreeSync 显示器(2560×1440、165Hz、100%sRGB、HDR400、Type-C 65W)

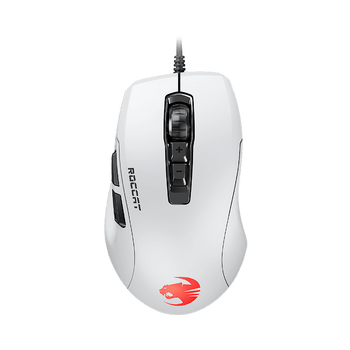

ROCCAT 冰豹 KONE PURE ULTRA 轻量版 有线鼠标 16000DPI RGB 白色

ROCCAT 冰豹 KONE PURE ULTRA 轻量版 有线鼠标 16000DPI RGB 白色

BOSE 博士 SoundLink Flex 便携蓝牙音箱 黑色

BOSE 博士 SoundLink Flex 便携蓝牙音箱 黑色

网友评论